表面有微結構的硅片鍵合技術

發布時間:2020-05-08

瀏覽次數:440

張棟鵬,蔡安江,周嘉瑋,翟彥昭

( 西安建筑科技大學 陜西省納米材料與技術重點實驗室,陜西 西安 710055)

摘 要: 針對表面帶有微結構硅晶圓的封裝展開研究,以采用 Ti / Au 作為金屬過渡層的硅—硅共晶鍵合為對象,提出一種表面帶有微結構的硅—硅共晶鍵合工藝,以親水濕法表面活化處理降低硅片表面雜質含量,以微裝配平臺與鍵合機控制鍵合環境及溫度來保證鍵合精度與鍵合強度,使用恒溫爐進行低溫退火,解決鍵合對硅晶圓表面平整度和潔凈度要求極高,環境要求苛刻的問題。高低溫循環測試試驗與既定拉力破壞性試驗結果表明: 提出的工藝在保證了封裝組件封裝強度的同時,具有工藝溫度低、容易實現圖形化、應力匹配度高等優點。

關鍵詞: 晶片鍵合; 帶有微結構硅晶圓; 共晶鍵合

中圖分類號: TP 212 文獻標識碼: A 文章編號: 1000—9787( 2019) 06—0056—03

Bonding technology of silicon wafer with micro-structure on surface

ZHANG Dongpeng,CAI Anjiang,ZHOU Jiawei,ZHAI Yanzhao

( Shaanxi Key Laboratory of Nano Materials and Technology,Xi’an University of Architecture & Technology, Xi’an 710055,China)

Abstract: A novel Si-Si wafer bonding method is presented to achieve micro-structured surface silicon wafer package. Ti / Au is chosen as metal transition layer to ensure the bonding force. Hydrophilic wet method is used for surface treatment and to reduce the surface impurity content,micro assembly platform and bonding machine are used to control the bonding environment and temperature to ensure both precision and strength of bonding.Silicon wafer is annealed by using constant temperature furnace. This method can achieve bonding with low level silicon wafer surface and the degree of cleanliness requirements,harsh environmental requirements. The results of high and low temperature cycle test and the established tensile failure test show that this method ensures the strength of the packaging module,and has the advantages of low process temperature,easy realization of graphics and high degree of stress matching.

Keywords: wafer bonding; micro-structured surface silicon wafer; eutectic bonding

0 引 言

封裝技術對微機電系統 (micro-electro-mechanical system,MEMS) 器件尺寸及功能的影響巨大,已成為 MEMS技術發展和實用化的關鍵技術[1]。實現封裝的技術手段很多,其中較關鍵的工藝步驟就是鍵合工藝。隨著 MEMS 技術的發展,越來越多的器件封裝需要用到表面帶有微結構的硅片鍵合,然而MEMS器件封裝一般采用硅—硅直接鍵合( silicon directly bonding,SDB) 技術[2]。由于表面有微結構的硅片界面已經受到極大的損傷,其平整度和光滑度遠遠達不到SDB的要求,要進行復雜的拋光處理,這大大加大了工藝的復雜性和降低了器件的成品率[3]。

Abouie M 等人[4]針對金—硅共晶鍵合過程中凹坑對鍵合質量的影響展開研究,提出一種以非晶硅為基材的金—硅共晶鍵合工藝以減少凹坑的形成,但非晶硅的實際應用限制較大。康興華等人[5]加工了簡單的多層硅—硅結構,但不涉及對準問題,實際應用的價值較小。陳穎慧等人[6]以金— 硅共晶鍵合技術對 MEMS 器件進行了圓片級封裝[6],其鍵合強度可以達到 36 MPa,但鍵合面積以及鍵合密封性不太理想,不適用一些敏感器件的封裝處理。袁星等人[7]對帶有微結構的硅—硅直接鍵合進行了研究,但其硅片不涉及光刻、深刻蝕、清洗等對硅片表面質量影響較大的工藝,故其鍵合工藝限制較大。

目前關于晶片鍵合的研究很多,工藝日漸成熟,但是對于表面帶有微結構的硅片鍵合研究很少,鍵合效果很差。

本文針對表面帶有微結構硅晶圓的封裝問題,提出一種基于采用 Ti / Au 作為金屬過渡層的硅—硅共晶鍵合的鍵合工藝,實現表面帶有微結構硅晶圓之間的鍵合,解決鍵合對硅晶圓表面要求極高,環境要求苛刻的問題。

1 鍵合試驗

1.1 鍵合理論

共晶鍵合[8,9]是利用某些共晶合金熔融溫度較低的特點,以其作為中間鍵合介質層,通過加熱熔融產生金屬—半導體共晶相來實現。因此,中間介質層的選取可以很大程度影響共晶鍵合的工藝以及鍵合質量。中間金屬鍵合介質層種類很多,通常有鋁、金、鈦、鉻、鉛—錫等。雖然金—硅共熔溫度不是最低( 363 ℃ ) 的,但其共晶體的一種成分即為預鍵合材料硅本身,可以降低鍵合工藝難度,且其液相粘結性好,故本文采用金—硅合金共晶相作為中間鍵合介質層進 行表面有微結構的硅—硅共晶鍵合技術的研究。而金層與 硅襯底的結合力較弱,故還要加入鈦金屬作為黏結層增強金層與硅襯底的結合力,同時鈦也具有阻擋擴散層的作用, 可以阻止金向硅中擴散[10,11]。

表面帶有微結構硅晶圓的界面已受到極大的損傷,其表面粗糙度遠高于拋光硅片( Ra < 0. 5 nm) ,有時甚至可以達到 1 μm 以上。金硅共晶鍵合時將金薄膜置于欲鍵合的兩硅片之間,加熱至稍高于金—硅共晶點的溫度,即 363 ℃ , 金硅混合物從預鍵合的硅片中奪取硅原子,達到硅在金硅二相系( 其中硅含量為 19 % ) 中的飽和狀態,冷卻后形成良好的鍵合[12,13]。而光刻、深刻蝕、清洗等工藝帶來的雜質對于金硅二相系的形成有很大的影響。以表面粗糙度極高且有雜質的硅晶圓完成鍵合,達到既定的鍵合質量成為研究重點。

1.2 試驗方案

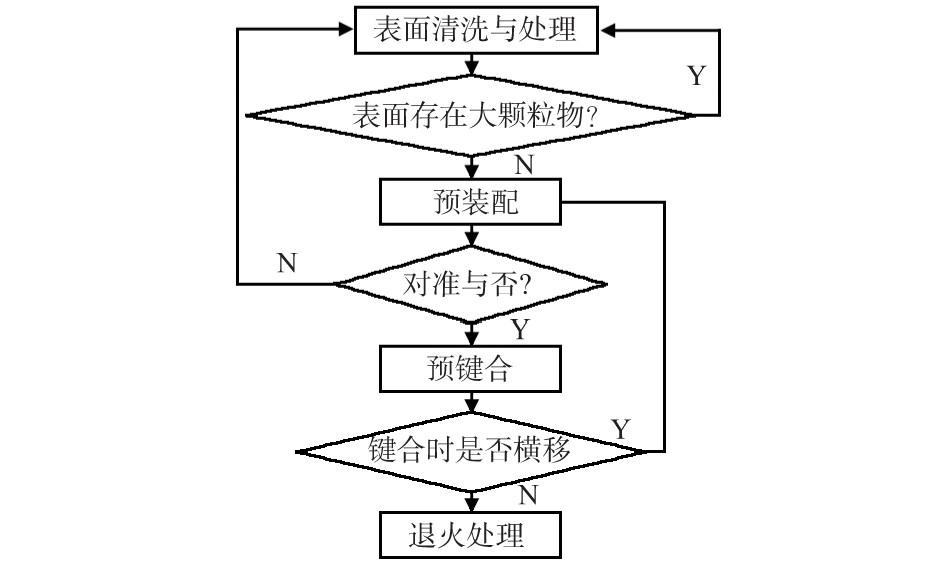

本文采用封裝組件的上下板與中間可動件為材料進行雙面濺金鍵合試驗,通過不斷改善表面清洗及處理工藝和 預鍵合工藝,實現表面有微結構的硅—硅鍵合,確定合適的鍵合工藝參數,為后續的工藝優化與改良打下基礎。設計的鍵合主要流程如圖 1 所示。

圖1 硅-硅鍵合主要工藝流程

2.1 表面清洗和親水處理

硅—硅鍵合表面清洗和處理方法分為親水處理與疏水處理兩種,本文采用親水處理方法,其工藝較簡單:

1) 丙酮超聲清洗 5 min,去離子水清洗,氮氣吹干;

2) 120 ℃ 濃硫酸雙氧水混合( SPM) 溶液( 濃 H2 SO4 ∶H2O2= 3∶ 1) 浸泡處理 10 min,去離子水清洗,氮氣吹干;

1) 70 ℃ 氨水雙氧水混合( RCAI) 溶液( NH4 OH∶ H2 O2 =1∶ 1) 浸泡處理 15 min,去離子水清洗,氮氣吹干。

2.2 預鍵合

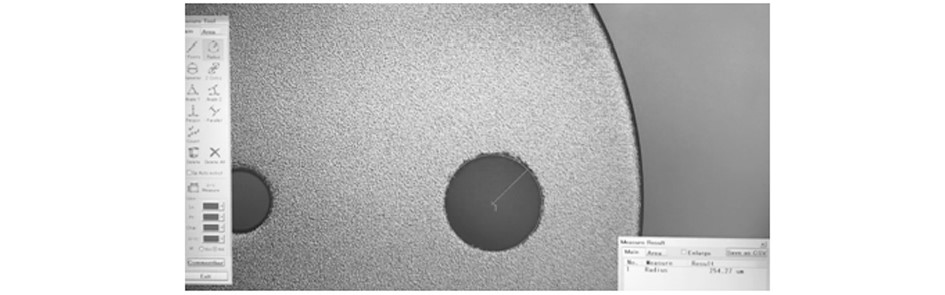

1) 在預鍵合表面濺射一層 30 nmTi 薄膜,再濺射一層200 nmAu 薄膜,濺射完成后如圖 2 所示。

圖 2 濺射完成后預鍵合晶片

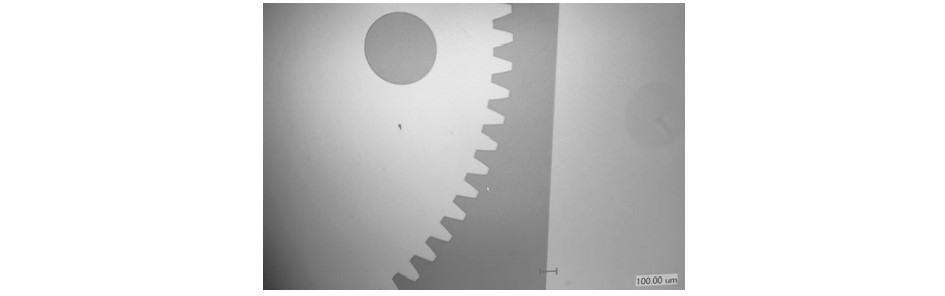

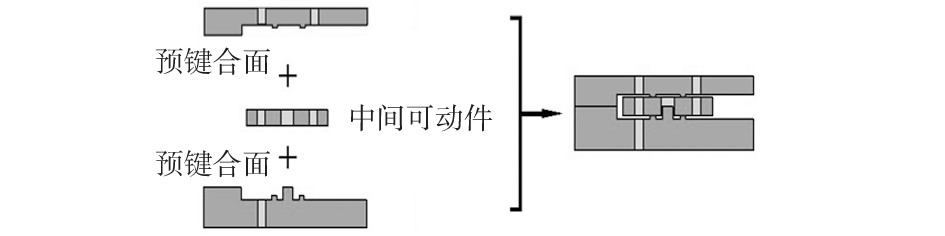

2) 將預鍵合晶片與中間可動件( 圖 3) 在微裝配平臺上進行預裝配( 圖 4) 。

圖 3 中間可動件

圖 4 預裝配示意

3) 將預裝配好的組件緊貼在一起放入鍵合臺上,設定壓力為 40 kPa,加熱至 363 ℃ ,保溫 10 min,隨后加熱至 380 ℃ ,保溫 15 min,自然降溫。

2.3 退火處理

將預鍵合好的 Si 片在氮氣的保護下進行快速退火處理,退火溫度為 300 ℃ ,退火時間為 15 min。

2 結果分析

顯微鏡下可以觀測到有些樣片上下板之間有間隙,原 因為從微裝配平臺轉移至鍵合臺的過程可能導致結構對準 出現偏差,影響鍵合效果。

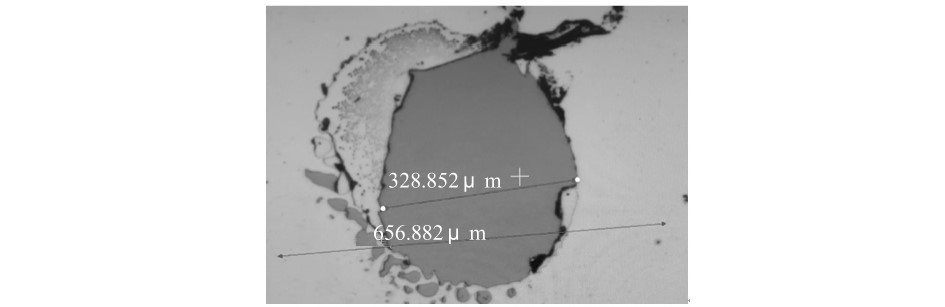

取其中 5 片進行檢測,在既定拉力下均未分開,加大拉力進行破壞性檢測,得到破損的鍵合面( 圖 5) 。

由圖可以看出實驗樣品存在的鍵合類型有兩種:

1) 在金—硅界面發生的共晶鍵合

金—硅界面在高于其共晶溫度 363 ℃ 時生成金硅化合物。該過程對金、硅的質量比例要求極其嚴格,硅含量略微 偏離 19 % ,其共晶溫度就立刻上升。

圖 5 破損的鍵合面

2) 在互相接觸的金—金界面發生的熱壓鍵合

在對金層施加一定的壓力和溫度時,金層發生流動、互 融,從而形成鍵合。該過程對金的純度要求較高,即當金層 發生氧化就會影響鍵合質量。

將剩余 5 片置入恒溫爐中進行高低溫循環測試,隨后在既定拉力下進行檢測,樣片均未分開。破壞性測試后,可 觀測到樣片鍵合率在 10 % 左右,低于標準水平。

3 結 論

1) 由既定拉力測試高低溫循環測試結果可以看出,該鍵合工藝在滿足實際應用所需鍵合強度的同時,解決了鍵合對硅晶圓表面平整度和潔凈度要求極高、對環境要求苛刻的問題。

2) 由高低溫循環測試結果可以看出,該鍵合工藝可以適應復雜的實際應用環境,且具有工藝溫度低,容易實現圖 形化,應力匹配度高等優點。

3) 由破壞性試驗結果可以看出,該鍵合工藝在圖形邊沿的鍵合率并不高,鍵合效果不太理想,還需對工藝流程進 一步優化,對工藝參數進行改進,以期達到更高的鍵合強度與鍵合率。

參考文獻:

[1] TEE T Y,FAN X J,LAI Y S. Advances in wafer level packaging ( WLP) [J]. Microelectronics Reliability,2010,50 ( 4 ) : 479 - 480.

[2] TONG Q Y. Low temperature wafer direct bonding[J]. J MEMS,1994,31: 29 - 35.

[3] CHENG Y T,LIN L W. Localized silicon fusion and eutectic bonding for MEMS fabrication and packaging[J]. J MEMS, 2000,9: 3 - 8.

[4] ABOUIE M,LIU Q,IVEY D G. Eutectic and solid-state wafer bonding of silicon with gold[J]. Materials Science & Enginee- ring B,2012,177( 20) : 1748 - 1758.

[5] 康興華. 多層硅直接鍵合技術的研究[D]. 南京: 東南大學,2011.

[6] 陳穎慧,施志貴,鄭英彬,等. 金—硅共晶鍵合技術及其應用[J]. 納米技術與精密工程,2015( 1) : 69 - 73.

[7] 袁星,陶智,李海旺,等. 從雙層到多層帶有微結構的硅硅直接鍵合技術研究[J]. 航空動力 學 報,2016,31 ( 11 ) : 2628 -2634.

[8] 王翔,張大成,李婷,等. 壓阻加速度計的 Au-Si 共晶鍵合[J].半導體學報,2003,24( 3) : 332 - 335.

[9] 張東梅,丁桂甫,汪紅,等. MEMS 器件氣密性封裝的低溫共晶鍵合工藝研究[J]. 傳感器與微系統,2006,25( 1) : 82 - 84.

[10] TONG Q Y. Low temperature wafer direct bonding[J]. Journal of Microelectromechanical Systems,1994,3( 1) : 29 - 35.

[11] WOLFFENBUTTEL R F. Low-temperature intermediate Au-Si wafer bonding eutectic or silicide bond[J]. Sensors and Actuators A: Physical,1997,62( 1 /2 /3) : 680 - 686.

[12] JING E R,XIONG B,WANG Y L. The interface of Au / Si eutec- tic bonding studied by IR microscope[J]. Materials Letters, 2010,64( 7) : 827 - 829.

[13] 陳繼超,趙湛,杜利東,等. 利用銀錫共晶鍵合技術的 MEMS 壓力傳感器氣密封裝[J]. 納米技術與精密工程,2013, 11( 2) : 174 - 178.

作者簡介:

張棟鵬( 1994 - ) ,男,碩士,主要研究方向為微納執行器件,E—mail: 296387731@ qq. com。

蔡安江( 1965 - ) ,男,教授,博士研究生導師,研究領域為機械制造。

(聲明:本文為技術引用,侵權請聯系刪除)

滬公網安備 31011502016664號

滬公網安備 31011502016664號

唐女士-華南、西南

唐女士-華南、西南